PIM 활용성 향상에 기여할 것으로 기대

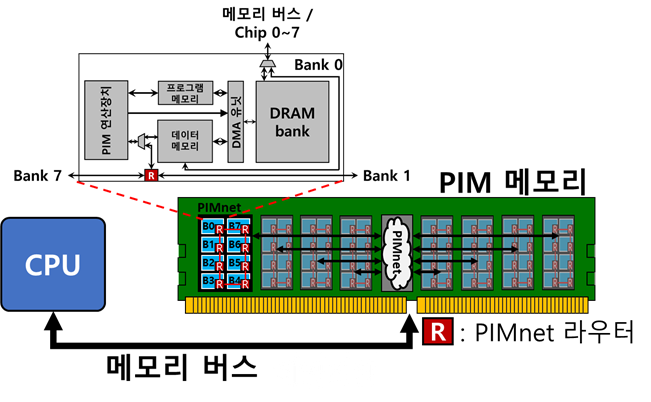

PIM 특화 인터커넥트를 적용한 PIM 연산장치 간 통신 개념도. ⓒ한국과학기술원

PIM 특화 인터커넥트를 적용한 PIM 연산장치 간 통신 개념도. ⓒ한국과학기술원

한국과학기술원(KAIST)은 최대 11배 빨라진 PIM 반도체 네트워크를 개발했다고 19일 밝혔다.

김동준 KAIST 전기및전자공학부 교수 연구팀은 미국 노스이스턴 대학, 보스턴 대학와 스페인 무르시아 대학 저명 연구진과‘PIM 반도체 간 집합 통신에 특화된 인터커넥션 네트워크 아키텍처’를 통한 공동연구로 PIM 반도체의 통신 성능을 비약적으로 향상하는 기법을 개발했다.

김동준 교수 연구팀은 기존 PIM 반도체가 갖는 메모리 내부 연산 장치 간 통신 구조의 한계를 밝혔다. 기존에 메모리 내부에 존재하는 데이터 이동을 위한 버스 구조를 최대한 활용하면서 각 연산장치를 직접적으로 상호 연결하는 인터커넥션 네트워크 구조를 적용함으로써 PIM 반도체의 통신 성능을 극대화하는 기법을 제안했다.

이를 통해 PIM 반도체를 위한 연산 과정에서 통신 처리를 위한 CPU의 개입을 최소화해 PIM 반도체 시스템의 전체적인 성능과 활용성을 높인 PIM 반도체에 특화된 인터커넥션 네트워크 구조를 개발했다.

메모리 공정은 복잡한 로직의 추가가 어렵다는 문제점이 있는데 김동준 교수팀이 개발한 네트워크 구조는 PIM에서 비용 효율적인 인터커넥트를 구현했다.

이 구조는 병렬 컴퓨팅과 기계학습 분야에서 널리 활용되는 집합 통신 패턴에 특화돼 있으며, 각 연산장치의 통신량과 데이터 이동 경로를 미리 파악할 수 있다는 집합 통신의 결정성 특징을 활용해 기존 네트워크에서 비용을 발생시키는 주요 구성 요소들을 최소화시켰다.

기존 PIM 반도체들이 통신하기 위해서는 CPU를 거쳐야만 하기 때문에 상당한 성능 손실이 있었다.

하지만 연구팀은 PIM 특화 인터커넥션 네트워크를 적용하면 기존 시스템 대비 어플리케이션 성능을 최대 11배 향상했다. 그 이유는 PIM 반도체의 내부 메모리 대역폭 활용률을 극대화하고 PIM 메모리 시스템의 규모가 커짐에 따라 통신 성능의 확장성이 함께 증가했기 때문이다.

김동준 교수는 “데이터 이동을 줄이는 것은 PIM을 포함한 모든 시스템 반도체에서 핵심적인 요소”라며 “PIM은 컴퓨팅 시스템의 성능과 효율성을 향상할 수 있지만 PIM 연산장치 간 데이터 이동으로 인해 성능 확장성이 제약될 수 있어 응용 분야가 제한적이고, PIM 인터커넥트가 이에 대한 해법이 될 수 있다”고 설명했다.